JTAG на службе специалиста по безопасности

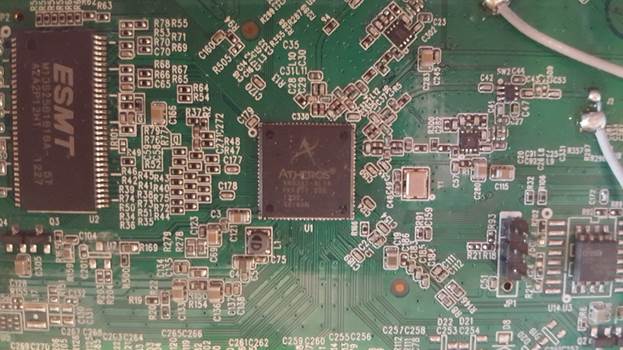

Представьте, что вы держите в руках устройство подобное тому, которое показано на рисунке ниже, и вас просят получить полный доступ к системе этого устройства. С чего вы начнете?

Автор: Senrio

Представьте, что вы держите в руках устройство подобное тому, которое показано на рисунке ниже, и вас просят получить полный доступ к системе этого устройства. С чего вы начнете? (если хотите увидеть, как добываются права суперпользователя к роутеру, сразу переходите к разделу «Реализация атаки: получение полного доступа к домашнему роутеру»).

Рисунок 1: Наша цель: ОЧЕНЬ популярная модель пользовательской точки доступа

Поскольку имеется неограниченный физический доступ к устройству, возможно, у вас появится мысль об атаке непосредственно на аппаратную часть. С другой стороны, если у вас недостаточно опыта в этой области, могут возникнуть разные сомнения и вопросы. В данной статье будет представлена фундаментальная информация об использовании интерфейса JTAG для исследования оборудования. Кроме того, мы рассмотрим пример, иллюстрирующий преимущества прямого доступа к аппаратной части.

Почему производители используют JTAG?

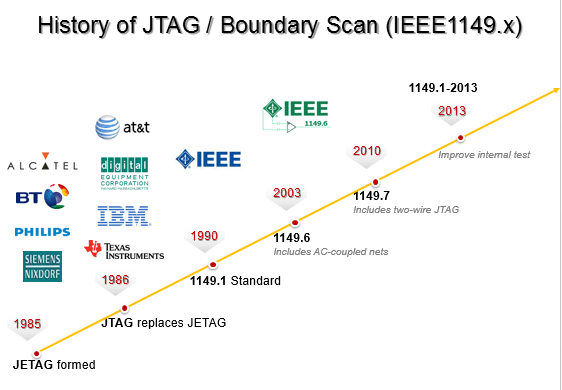

Рисунок 2: История развития JTAG

JTAG – распространенный аппаратный интерфейс для прямой связи компьютера с чипами на плате. Первая версия интерфейса была разработана консорциумом Joint (European) Test Access Group в середине 80-х годов вследствие постоянного усложнения методов тестирования печатных плат. JTAG начал приобретать популярность с тех пор, когда стал использоваться в процессорах Intel 80486 в 1990 году и стал соответствовать стандарту IEEE 1491 (в том же году). В наши дни JTAG используется для отладки, программирования и тестирования практически всех встроенных устройств.

Периферийное сканирование

Рисунок 3: Пины, используемые при периферийном сканировании

С изобретением интегральных микросхем появилась необходимость в тестировании соединений. Задача формулировалась так: нужно выяснить, что «Точка А» на плате корректно подсоединена к «Точке С». По мере того как индустрия двигалась в сторону увеличения плотности соединений и уменьшения размера компонентов, появилась необходимость в разработке стандартизированного способа тестирования интегральных микросхем (или «чипов»). Далее в микросхемы начали внедрять тестовую логику и ограничивать физический интерфейс до нескольких сигналов. В итоге появилось элегантное решение в виде интерфейса JTAG и периферийного сканирования, предназначенных для тестирования, отладки и диагностики современных электронных систем. Попросту говоря, периферийное сканирование позволяет читать и записывать отдельные биты на отдельные пины отдельных чипов на плате. Чтение и запись единиц и нулей напрямую на пины – чрезвычайно полезная возможность. Однако зачастую возникает и непонимание сути данного вопроса.

Рисунок 4: Выводы интегральной микросхемы

Интерфейс JTAG позволяет производителю тестировать физические соединения между пинами на чипе. Когда инженер говорит об использования JTAG для «отладки» платы, подразумевается нечто совсем другое, чем традиционная отладка приложения. В данном случае говорится о тестирование пина А у чипа А на предмет корректного соединения с пином Б чипа Б и того, что данные пины функционируют корректно. Поскольку JTAG дает прямой доступ к аппаратной части, данный интерфейс является отличным инструментом для исследования безопасности устройства.

Основы JTAG

Рисунок 5: Базовая схема JTAG

Перед тем как рассматривать JTAG как инструмент исследователя, поговорим про основы.

4 пина, плюс 1

Официальный стандарт требует для JTAG наличия 4 пинов (или сигналов) и одного необязательного (пятого). Эти сигналы и небольшие части кремниевой логики, которые подсоединены к тем пинам в целях управления, в общем, обозначаются как порт доступа к средствам тестирования (Test Access Port) или TAP-контроллер.

JTAG – «Вавилонская башня»

При изучении методов работы с JTAG приходится сталкиваться с огромным количеством информации, сбивающей с толку. Сайты производителей рассказывают «теорию» о том, как работает JTAG, и умалчивают о практических аспектах. Существуют и другие факторы, которые вносят еще больше путаницы:

- Использование сленга: а конкретно словосочетания «информационная безопасность. Все толкуют об информационной безопасности, но мало кто дает рабочие методики.

- Разночтения термина JTAG: термин JTAG означает разное для разных групп людей. Например, в сообществе геймеров «JTAG» означает аппаратную модификацию консоли, позволяющую играть в пиратские игры или загружать доморощенный контент. Сей факт затрудняет поиск полезной информации.

- Разночтения родственных терминов: как упоминалось ранее, когда электроинженер говорит об «отладке», то подразумевает следующее: «Все ли пины на правильных местах? Достаточно мощности? Корректно ли работает логика цепи?». Когда программист упоминает об «отладке», то подразумевает отладчик GDB или WinDBG. JTAG разработан для тестирования аппаратной части, а не программной.

- Недопонимание: для программистов наиболее близкая область, похожая на работу с JTAG, - отладка ядра через отладочный кабель (USB, Parallel или Serial). Однако данное сравнение некорректно, поскольку даже в этом случае происходит отладка кода, запускаемого на удаленной системе, и передача команд по отладочному кабелю. В случае с JTAG происходит работа исключительно с аппаратной частью.

Чем JTAG не является!

В целях рассеивания дезинформации (звучит угрожающе) ниже рассказывается о том, чем JTAG не является:

- Специфическим устройством для отладки прошивки и аппаратной части.

- Приложением для отладки кода на устройстве.

- Протоколом. В спецификации на JTAG не указана схема информационного обмена между отладчиком и целевой системой (то есть нет .h файла, описывающего «JTAG-пакет», передаваемый по серийному, параллельному или USB-кабелю).

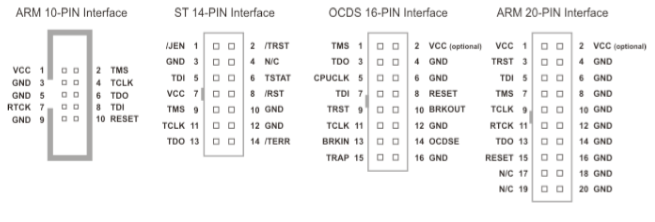

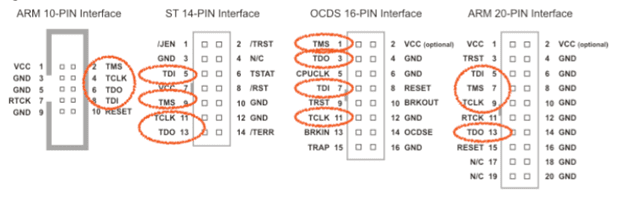

- Коннектором. В отличие от спецификаций для USB и Ethernet в стандарте JTAG не указано, как должны выглядеть коннекторы, что приводит к ОЧЕНЬ большой путанице касательно «JTAG» коннекторов. Особенно в среде программистов. Представьте, если бы каждый USB-кабель был различным.

Рисунок 6: Все модели, показанные на рисунке, можно отнести к «JTAG» коннекторам

Рисунок 7: JTAG-коннектор для роутера с прошивкой DD WRT

Рисунок 8: JTAG-коннектор для кассового аппарата

Все коннекторы, показанные на рисунке выше, относятся к JTAG-коннекторами. Но почему они выглядят по-разному? Где стандартизация? На практике вы можете столкнуться с сотнями и тысячами различных JTAG-коннекторов. Почему? Прежде чем ответить на этот вопрос, рассмотрим, что такое интерфейс JTAG, согласно стандарту. А согласно спецификации 1149 в JTAG-коннекторе должно быть 5 пинов (или сигналов):

- TCK: Test Clock (тестовая синхронизация)

- Играет роль метронома, задающего скорость TAP-контроллера. На данном пине просто пульсирует напряжение в определенном постоянном ритме. При каждом биении TAP-контроллер выполняет одно действие. Частота в стандарте не указана и зависит от внешнего устройства, которое управляет интерфейсом JTAG.

- TMS: Test Mode Select (выбор тестового режима)

- Посредством манипуляции напряжением на данном пине мы управляем деятельностью интерфейса JTAG.

- TDI: Test Data-In (входные тестовые данные)

- Пин, передающий информацию на чип. В стандарте не определен протокол для передачи через данный пин. Решение о выборе протокола принимает производитель. Функция интерфейса JTAG – только передать нули и единицы на чип.

- TDO: Test Data-Out (выходные тестовые данные)

- Пин, предназначенный для вывода информации с чипа. Так же как и в пине TDI протокол передачи в стандарте не определен.

- TRST: Test Reset (необязательный)

- Опциональный пин, используемый для сброса JTAG в начальное состояние. Далее будет объяснено, почему этот пин является необязательным.

Теперь, когда мы познакомились с назначением пинов/сигналов, взглянем еще раз на коннекторы, показанные выше:

Рисунок 9: Каждый коннектор имеет пины, имеющие отношение к JTAG

Сейчас мы понимаем, что каждый коннектор, строго говоря, не является JTAG-коннектором, а лишь имеет набор сигналов, имеющих отношение к интерфейсу JTAG. Именно при помощи данных сигналов мы можем манипулировать и общаться с машиной состояний (state machine) целевого устройства через TAP (Test Access Port) контроллер, встроенный в кристалл.

Примечание: машина состояний интерфейса JTAG настолько проста, что вы можете записать Arduino-код для организации последовательного соединения при помощи программной эмуляции (технология bit-banging).

Машина состояний интерфейса JTAG

В спецификации IEEE 1149.1 указаны не только сигналы, но и модель поведения «Машины состояний», которая встроена в TAP-контроллер устройства. Диаграмма контроллера состояний показана в левом верхнем углу на видео ниже. Манипуляцией напряжением на пине TMS у TAP-контроллера и пине TCK мы можем управлять алгоритмом, при помощи которого Машина изменяет состояния. При каждом такте часов TAP-контроллер на целевом устройстве проверяет, есть ли напряжением на пине TMS и интерпретирует данный сигнал как 1 (есть напряжение) и 0 (нет напряжения). Эта серия единиц и нулей перемещает интерфейс JTAG через относительно простую машину состояний. Данная машина состояний настолько проста, что вы можете записать Arduino-код в целях различных манипуляций. Значение пина TMS, необходимое для изменения состояния, обозначено крошечными «1» и «0» на диаграмме машины состояний. Операции машины состояний можно найти на анимации ниже.

Видео 1: Механика работы машины состояний интерфейса JTAG (в очень упрощенном виде). В действительности дискретизация сигнала немного отличается (дискретизация сигналов при нарастающем и спадающем фронте происходит по-разному). Кроме того, визуализация тактового сигнала, показанного выше, немного барахлит. В один цикл машина состояний выполняет только одну операцию. Дискретизация происходит при каждом цикле.

Обратите внимание, что информация читается и передается с пинов TDI и TDO в то время, когда машина состояний находится в состояниях Shift-IR и Shift-DR. Отличия между этими состояниями и соответствующими регистрами выходит за рамки этой статьи. Скажем лишь, что регистр инструкций IR и регистр данных DR похожи на вызовы функций. Значение в регистре IR определяет «функцию», в регистре DR – «аргумент». В спецификации для JTAG информации на этот счет нет. Конкретную функцию определяет производитель.

Видео 2: Анимация TAP-контроллера, работающего в режиме «Железнодорожной станции». По пинам TDI/TDO (путям) происходит передача через регистр (платформу).

Интересно отметить, что если на пине в течение 5 циклов подряд висит 1, то вы сразу же попадаете в состояние «Test Logic – Reset» (обнуление тестовой логики). Если пин TRST не используется, то этим методом можно сбрасывать TAP-контроллер в базовое состояние, вследствие чего, как упоминалось выше, пин TRST является необязательным.

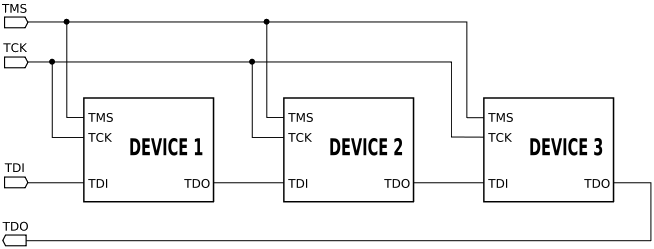

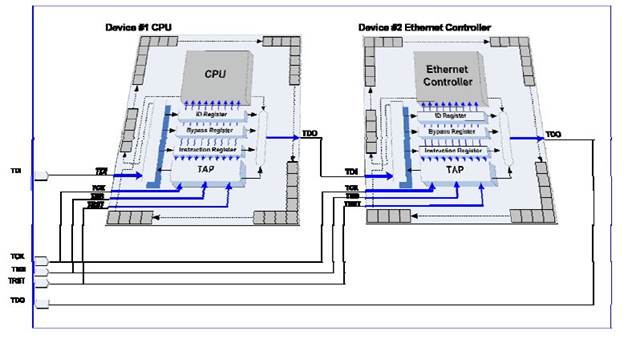

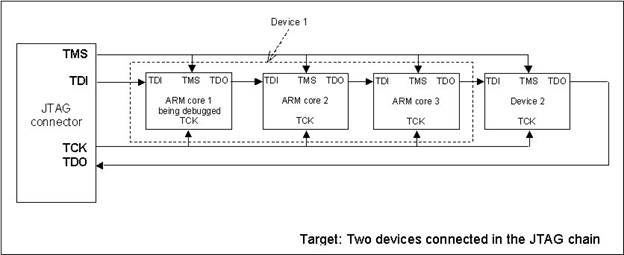

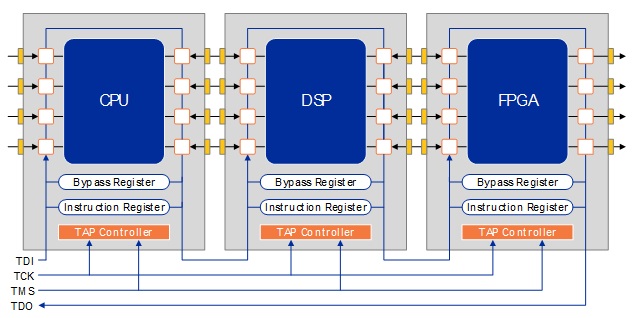

Наконец, следует учитывать, что интерфейсы JTAG нескольких чипов на одной плате могут быть объединены в одну цепь и имеют общие выводы. То есть тестирование каждого чипа можно пользоваться данным объединенным набором. Данная схема особенно интересна в отношении однокристальных систем (System-On-Chip; SoC), где множество компонентов (ethernet, wifi, bluetooth и т. д.) объединены в один чип. Зачастую JTAG-цепь объединяет несколько ядер внутри одного чипа.

Рисунок 10: Примеры объединения нескольких устройств или нескольких ядер внутри одного чипа

Исследование безопасности при помощи JTAG

Как вы уже знаете, в целях предоставления инженерам и разработчикам простого способа для тестирования и программирования был придуман интерфейс JTAG. С другой стороны, если вы разработаете суперсовершенный замок и оставите ключ под ковриком, ваша дверь будет закрытой ровно до тех пор, пока кто-нибудь не узнает где лежит ключ. В случае с JTAG ситуация примерно похожая. По сути, этот интерфейс дает злоумышленникам простой способ найти ключи от сокровищницы. Давайте рассмотрим, чем JTAG может быть полезен для специалиста по безопасности.

JTAG – простой и прямолинейный интерфейс

Вначале не лишним будет напомнить, что JTAG – это просто интерфейс, который не учитывает внутреннее устройство чипа. То есть взломать устройство только при помощи JTAG технически возможно, но на практике потребует слишком много времени, поскольку необходимо разобраться с внутренним устройством. Чтобы JTAG стал эффективным инструментом, потребуется нечто, что может преобразовывать информацию, пригодную для чтения человеком, в низкоуровневые инструкции входящие и выходящие из TAP-контроллера. Воспользоваться всей мощью JTAG позволяет отладчик OpenOCD.

Рисунок 11: Домашняя страница отладчика OpenOCD

OpenOCD – единственный репозиторий с открытым исходным кодом (база знаний) для различных чипов и интерфейсов. OpenOCD в сочетании с интерфейсом JTAG может управлять TAP-контроллером на целевом устройстве, отсылая биты (через машину состояний, описанную выше), которые затем чип интерпретирует как корректные команды.

Отладка аппаратной части при помощи софта

Запуск OpenOCD поверх интерфейса JTAG позволяет останавливать и пошагово проходить операции, инспектировать память, писать байты напрямую в память, устанавливать точки останова и наблюдения и даже инжектировать код в процесс или память. По сути, мы управляем аппаратной частью, выполняя стандартные отладочные задачи при помощи софта. Более того, OpenOCD позволяет использовать традиционные отладочные утилиты через GDB-сервер, позволяя отлаживать прошивки и софт в устройства при помощи GDB, IDA Pro и других приложений, которые могут работать как GDB-клиент.

Конфигурационные файлы

Здесь возникает закономерный вопрос. Как при всем обилии архитектур и чипов OpenOCD может взаимодействовать со всеми? Попросту говоря, OpenOCD использует специальные конфигурационные файлы для изучения инструкций, которые понимают устройства. Настроечные файлы обучают OpenOCD как правильно управлять TAP-контроллером, используемого под конкретную архитектуру. Соответственно, у вас должен быть корректный конфигурационный файл под тот чип, с которым вы хотите работать. Наиболее распространенные конфигурации уже включены в состав OpenOCD, а другие легко загрузить из репозитария.

Дополнительное оборудование

Большинство компьютеров не имеют встроенного оборудования для взаимодействия с JTAG. Для решения эти задач вполне подойдут устройства наподобие Shikra или BusPirate, которые легко можно купить в интернете.

Рисунок 12: Shikra – устройство для исследования аппаратной части

Профессиональное оборудование имеет больше плюсов: лучший контроль над процессом и большую производительность. Часто в составе подобных комплексов есть собственный отладчик. Однако и стоимость возрастает пропорциально. При использовании OpenOCD вам лишь нужен конфигурационный файл, который «обучит», как правильно взаимодействовать с устройством. Обычно коммуникация между компьютером и JTAG-контроллером происходит через последовательный интерфейс.

Недооцененный метод проникновения

Надеемся, что вы уже начали понимать потенциальные последствия после получения доступа к интерфейсу JTAG. Если все настроено корректно, то вы, получаете неограниченные возможности, и, по сути, становитесь полным владельцем устройства. Вы можете просматривать и модифицировать информацию и выгружать содержимое RAM и FLASH-чипов. Несмотря на очевидные преимущества, зачастую специалисты по безопасности не обращают особого внимания на JTAG, предпочитая программные методы проникновения.

Реализация атаки: получение полного доступа к домашнему роутеру

Рисунок 13: Внутреннее устройство подопытного домашнего роутера

В качестве подопытного экземпляра мы взяли устройство, которое упоминалось в самом начале статьи. Производитель предусмотрел стандартную систему авторизации в целях недопущения запуска команд до тех пор, пока у вас не будет учетной записи. Информацию об аккаунте держится в секрете, и наша задача – получить доступ к роутеру во что бы то ни стало.

Примечание: как вы уже догадались, обход встроенной системы защиты и получение полного доступа и прав суперпльзователя мы будет осуществлять через интерфейс JTAG.

Подготовительная часть

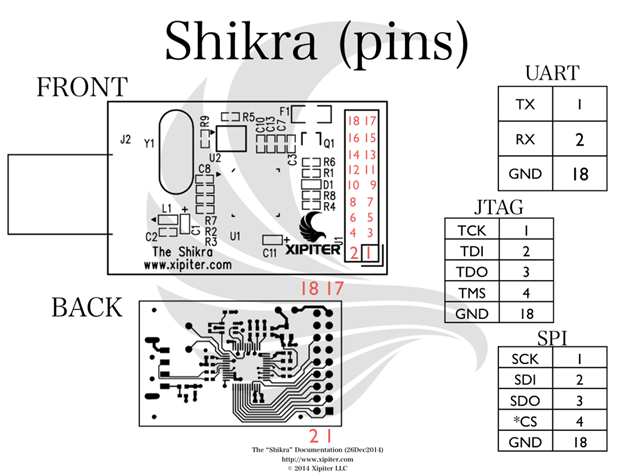

В нашем примере мы будем использовать устройство Shikra в качестве JTAG-контроллера и приложение OpenOCD в качестве отладчика, запущенного на виртуальной машине с OC Linux.

Рисунок 14: Назначение пинов устройства Shikra

- Подсоединяем кабель Serial-USB к UART-интерфейсу роутера, что позволит нам наблюдать за поведением устройства во время установки аппаратных битов.

- Включаем устройство и дожидаемся запроса на ввод логина и пароля. Именно данную защиту мы будем обходить с целью получения доступа к оболочке через UART-порт.

- Каждый пин Shikra подсоединяется к соответствующему пину роутера. Если вы не уверены, какой из пинов Data-In, а какой Data-Out, просто попробуйте разные подключения и в случае ошибки поменяйте включения местами. Назначение пинов, имеющие отношения к JTAG, на устройстве Shikra показаны на рисунке выше. Более детальную информацию по подключении Shirka можно найти в этой статье. Подключаем Shikra к USB-порту вашего компьютера, а затем физически соединяем пины Shirka и JTAG-интерфейса на роутере.

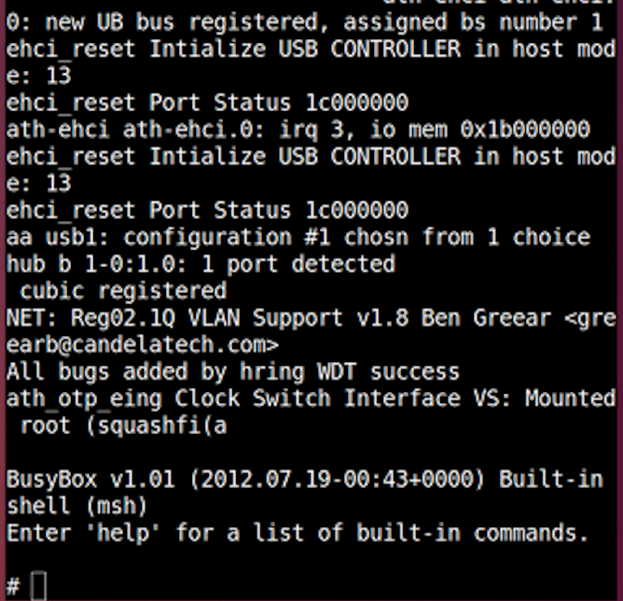

После подключения к UART-порту при включении роутера мы увидим процесс загрузки.

Видео 3: Загрузка роутера

Эмоциональное возбуждение быстро ослабевает при появлении запроса на ввод логина после полной загрузки устройства.

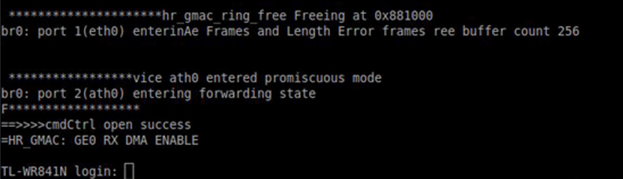

Рисунок 15: Запрос на ввод логина

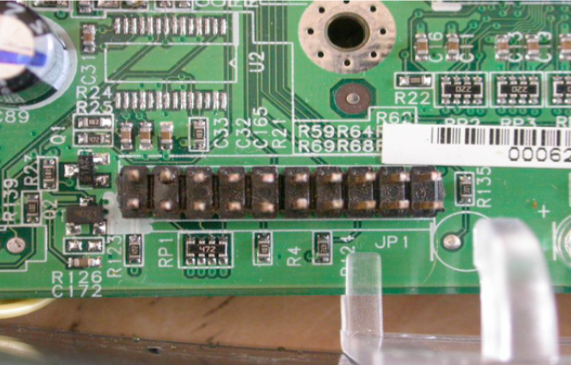

Далее мы рассмотрим, как использовать соединение с JTAG для обхода авторизации. Но вначале нужно найти этот самый интерфейс на роутере, что может оказаться непростой задачей. JTAG редко выводится наружу и вам, скорее всего, придется открыть крышку и залезть внутрь устройства.

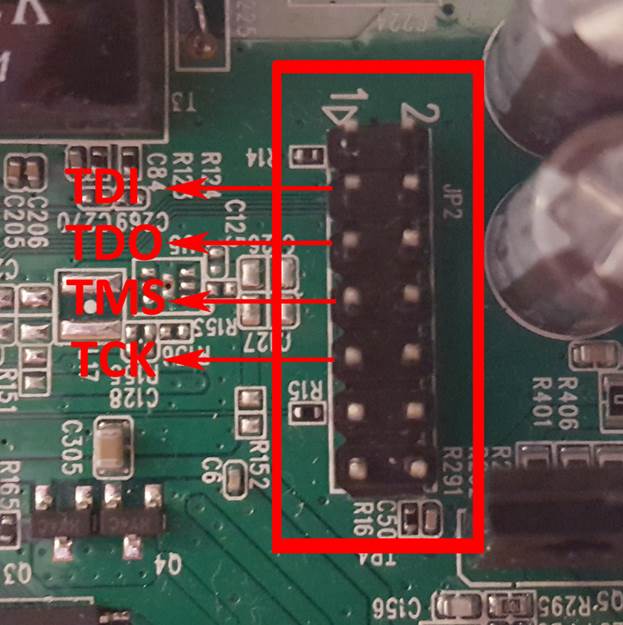

Рисунок 16: Интерфейс JTAG подопытной точки доступа

Иногда интерфейс виден сразу, а иногда производитель скрывает или вовсе удаляет соответствующие пины. Если пины интерфейса JTAG сразу найти сложно, обращайтесь к спецификации и технической документации. Если же документация недоступна, придется воспользоваться подручными средствами: вольтметром, логическим анализатором и устройством JTAGulator. В случае если производитель подошел к сокрытию интерфейса особо тщательно, возможно, вам потребуется паяльник.

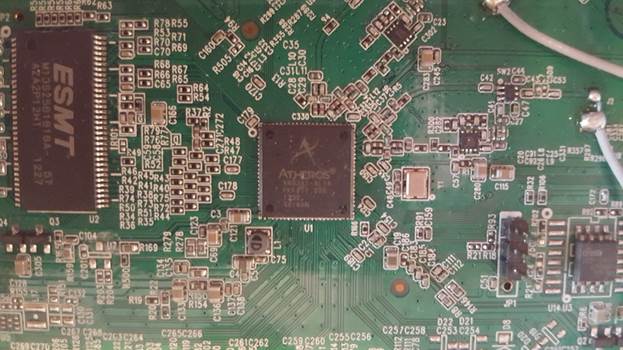

Рисунок 17: Микроконтроллер находится по центру платы

Получение полного доступа к системе

После подключения всех устройств полная схема будет выглядеть примерно так, как показано на рисунке ниже. Целевое устройство (точка доступа/роутер) подсоединено через «JTAG-интерфейс» (Shikra) к системе с программным обеспечением, предназначенным для взаимодействия с JTAG (OpenOCD и GDB).

Рисунок 18: Полная схема установки. Роутер подсоединен к компьютеру через устройство Shikra

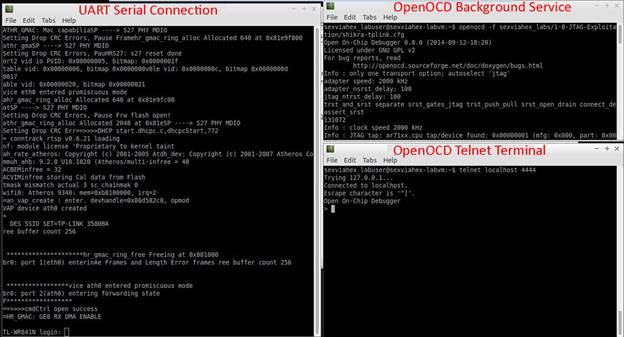

В итоге у нас перед глазами три терминала. Первый – последовательное соединение через UART-порт, предназначенный для отслеживания состояния роутера на случай возникновения ошибок или перезагрузки. Второй отображает информацию фоновой службы OpenOCD. Третий используется непосредственно для работы с отладчиком OpenOCD.

Рисунок 19: Три терминала для работы с сессией OpenOCD

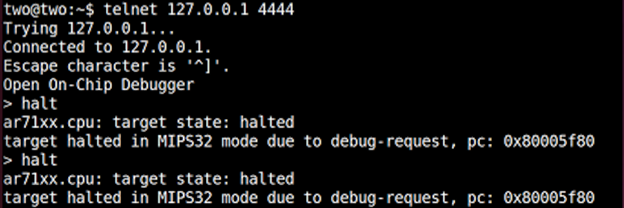

Первое, что необходимо сделать, остановить роутер при помощи команды halt. К сожалению, если посмотреть на терминал UART-порта, то можно увидеть, что через секунду после остановки роутер перезагружается. Подобное происходит потому, что в операционной системе работает функция Watchdog Timer, которая автоматически перезагружает устройство в случае остановки в течение определенного промежутка времени (обычно меньше секунды). Данная проблема обходится при помощи повторного ввода команды halt во время перезагрузки, пока функция Watchdog Timer еще не успела загрузиться. Поскольку наша задача изменить параметры загрузки, необходимо использовать команду halt перед стартом операционной системы.

Рисунок 20: Остановка роутера при помощи повторной команды halt

Остановив роутер, мы можем устанавливать точки останова, пошагово проходить операции и инспектировать/изменять память.

Рисунок 21: Выполнение различных команд в отладчике

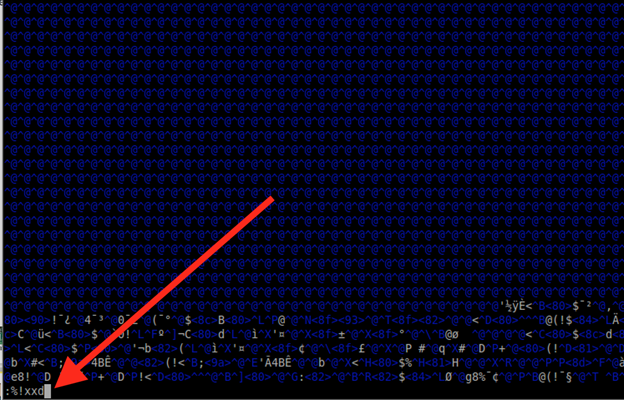

Чтобы получить полный доступ к роутеру, изменим в памяти аргументы загрузки так, чтобы роутер загрузился в режиме единичного пользователя. Для решения этой задачи нужно добавить пробел и цифру 1 в конец параметров загрузки. Чтобы посмотреть аргументы загрузки, воспользуемся извлеченным образом прошивки. Для переключения редактора Vim в режим шестнадцатеричного редактирования воспользуемся командой xxd.

![]()

Рисунок 22: Использование Vim в качестве шестнадцатеричного редактора

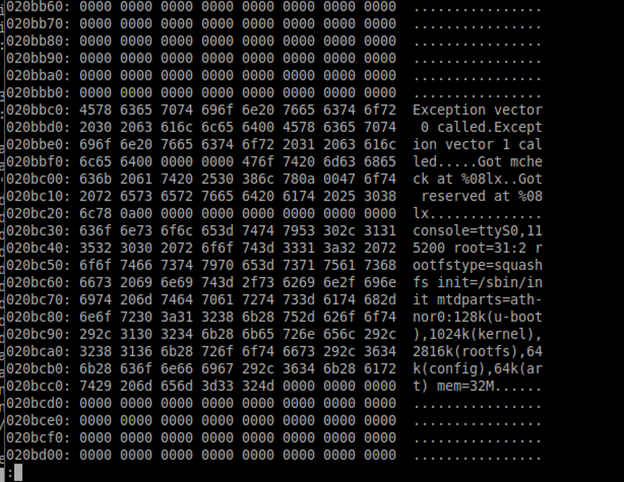

Рисунок 23: Место, где хранятся аргументы загрузки

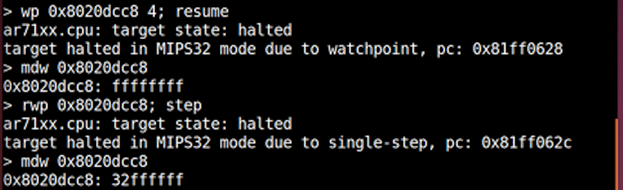

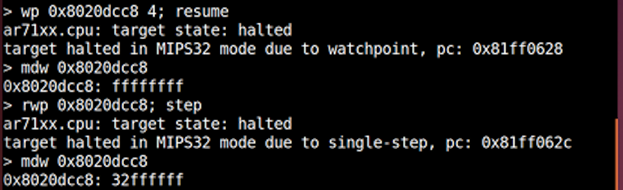

Исследуя извлеченную прошивку, находим адреса, где хранятся аргументы загрузки. Далее мы будем устанавливать точки наблюдения (watch point) на эту область памяти, где, весьма вероятно, будут находиться аргументы после распаковки ядра вскоре после загрузки. Данный трюк позволит нам не только отслеживать операции во время распаковки ядра, но и считывать аргументы перед загрузкой. Устанавливаем точки наблюдения на найденный адрес и возобновляем загрузку.

Рисунок 24: Установка точек наблюдения в то место, где будут находиться аргументы загрузки ядра

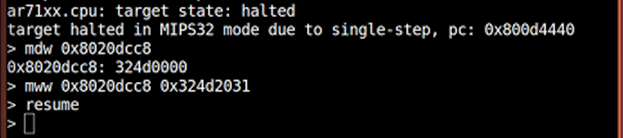

В процессе загрузки, как только дело дойдет до адреса, где установлена точка наблюдения, роутер опять остановится. После остановки в процессе распаковки ядра в память, мы можем дописать в конец параметров загрузки ядра последовательность "<пробел> 1" (или 0x2031, если перевести в шестнадцатеричный код). Затем удаляем точку наблюдения и позволяем роутеру завершить загрузку.

Рисунок 25: При помощи команд mdw (memory dump word; выгрузить слово из памяти) и mww (memory write word; записать слово в память) дописываем аргумент загрузки

После дописывания аргумента изменилась последовательность загрузки.

Рисунок 26: Шелл с правами суперпользователя

Теперь у нас есть шелл с правами суперпользователя, с которым можно работать через UART-интерфейс. Весь процесс занял около 15 минут.

Средства защиты

JTAG нужен производителю для решения разнообразных задач, начиная от проверки качества сборки и заканчивая загрузкой прошивки.

JTAG – невероятно полезен для производителей чипов при проектировании, тестировании и производстве и поэтому используется практически в каждом встроенном устройстве. С другой стороны, как было продемонстрировано в этой статье, JTAG представляет большую угрозу. Производители знают об этой проблеме и часто предпринимают шаги для ограничения доступа к JTAG. Способы защиты могут быть различными: сокрытие следов на плате или полностью удаление пинов. Во время производства провода, ведущие к интерфейсу, могут намеренно повредить. Данные методы в некоторой степени эффективны, но умелый злоумышленник с паяльником в руках практически всегда может восстановить повреждение. Некоторые стандарты рекомендуют использовать шифрование и криптографическую аутентификацию, но на практике эти методы используются крайней редко.

Заключение

Одно из железобетонных убеждений в IT-безопасности заключается в том, что если у злоумышленника есть неограниченный физический доступ к вашему оборудования, считайте, устройство вам уже не принадлежит. JTAG – технология, которая подтверждает истинность этого утверждения, и мы надеемся, что теперь вы понимаете почему.

Возможности, которые доступны через JTAG:

- Чтение и запись в память.

- Остановка выполнения прошивки (при помощи точек останова и наблюдения).

- Изменение инструкции и данных в памяти.

- Инжектирование инструкций напрямую в магистраль (pipeline) целевого чипа (без изменения памяти).

- Извлечение прошивки (для реверс-инжиниринга и поиска уязвимостей).

- Обход защитных механизмов (проверки шифрования, проверки паролей, контрольные сумму и т. д.).

- Нахождение скрытых JTAG-функций, которые могут намного больше, чем можно представить.

- и многое другое.

JTAG – чрезвычайно функциональный и полезный интерфейс для встроенных устройств. Разработчики, пишущие код для встроенных систем, обычно не подозревают о возможностях, которые доступны благодаря этой технологии. Мы видели множество систем, где разработчики тратили массу усилий на шифрование и защиту кода, даже не подозревая, что защита легко обходится на аппаратном уровне.

Естественно, в рамках одной статьи невозможно рассказать обо всем, но мы надеемся, что вы задумаетесь о тех бескрайних возможностях, которые доступны с JTAG.

Со всеми этими вездесущими отладочными интерфейсами, используемыми во встроенных устройствах, открываются двери для всех и каждого. Так как же защитить дверь, которая открыта? Занимайтесь мониторингом своего оборудования!

Отдельное спасибо Далин Макклеллан за помощь в подготовке статьи!

Домашний Wi-Fi – ваша крепость или картонный домик?